# Appendix I—The 8085 Instruction Set

# ACI data(8b)

**Description:** Add Immediate 8-bit data to the accumulator

with carry.

Bytes/M-Cycles/T-States: 2/2/7

Hex Code: CE

Flags: All flags are affected based upon the result of the addition.

## ADC R

**Description:** Add register to accumulator with carry.

Bytes/M-Cycles/T-States: 1/1/4

Register

Hex Codes: 8F A

88 B

89 C

8A D

8B E 8C H

8C H

8D L

Flags: All flags are affected based upon the result of the addition.

#### ADC M

**Description:** Add contents of memory location pointed to by HL register pair to the accumulator with carry.

Bytes/M-Cycles/T-States: 1/2/7

Hex Codes: 8E

Flags: All flags are affected based upon the result of the addition.

# ADD R

**Description:** Add register to accumulator.

Bytes/M-Cycles/T-States: 1/1/4

Register

Hex Codes: 87 A

80 B

81 C

82 D

83 E

84 H

85 L

Flags: All flags are affected based upon the result of the addition.

#### ADD M

**Description:** Add contents of memory location pointed to by HL to the accumulator.

Bytes/M-Cycles/T-States: 1/2/7

Hex Codes: 86

Flags: All flags are affected based upon the result of the addition.

## ADI data(8b)

**Description:** Add the immediate 8-bit data to the accumulator.

Bytes/M-Cycles/T-States: 2/2/7

Hex Codes: C6

Flags: All flags are affected based upon the result of the addition.

#### ANA R

**Description:** The contents of the accumulator and the register are logically ANDed and the result is put in the accumulator.

Bytes/M-Cycles/T-States: 1/1/4

# Register

A0 B

A1 C

A2 D

A3 E

A4 H

A5 L

**Flags:** S, Z, and P are modified based upon the result of the operation. CY is reset, and AC is set.

#### ANA M

**Description:** The contents of the accumulator and the contents of the memory location pointed to by HL are logically ANDed, and the result is put in the accumulator.

Bytes/M-Cycles/T-States: 1/2/7

Hex Codes: A6

**Flags:** S, Z, and P are modified based upon the result of the operation. CY is reset, and AC is set.

# ANI data(8b)

**Description:** The contents of the accumulator and the 8-bit data are ANDed and the result is put in the accumulator.

Bytes/M-Cycles/T-States: 2/2/7

Hex Codes: E6

**Flags:** S, Z, and P are modified based upon the result of the operation. CY is reset, and AC is set.

## CALL address(16b)

**Description:** The program sequence is transferred to the address specified by the 16-bit address. Before the program is transferred, the address of the instruction following the CALL instruction is pushed onto the stack.

Bytes/M-Cycles/T-States: 3/5/18

Hex Codes: CD

Flags: No flags are affected.

## CC address(16b)

**Description:** The program sequence is transferred to the address specified by the 16-bit address if the CY flag is set. If CY = 0, no transfer takes place. If the transfer takes place, the address of the instruction following the CC instruction is pushed onto the stack.

Bytes/M-Cycles/T-States: 3/2/9 if transfer is not taken

3/5/18 if the transfer is taken

Hex Codes: DC

Flags: No flags are affected.

# CNC address(16b)

**Description:** The program sequence is transferred to the address specified by the 16-bit address if the CY flag is not set. If CY = 1, no transfer takes place. If the transfer takes place, the address of the instruction following the CNC instruction is pushed onto the stack.

Bytes/M-Cycles/T-States: 3/2/9 if transfer is not taken

3/5/18 if the transfer is taken

Hex Codes: D4

**Flags:** No flags are affected.

# CP address(16b)

**Description:** The program sequence is transferred to the address specified by the 16-bit address if positive, or if the S flag = 0. If S = 1, no transfer takes place. If the transfer takes place, the address of the instruction following the CP instruction is pushed onto the stack.

Bytes/M-Cycles/T-States: 3/2/9 if transfer is not taken

3/5/18 if the transfer is taken

Hex Codes: F4

Flags: No flags are affected.

## CM address(16b)

**Description:** The program sequence is transferred to the address specified by the 16-bit address if minus, or if the S flag = 1. If S = 0, no transfer takes place. If the transfer takes place, the address of the instruction following the CM instruction is pushed onto the stack.

**Bytes/M-Cycles/T-States:** 3/2/9 if transfer is not taken

3/5/18 if the transfer is taken

Hex Codes: FC

## CPE address(16b)

**Description:** The program sequence is transferred to the address specified by the 16-bit address if parity is even, or the P flag = 1. If P = 0, no transfer takes place. If the transfer takes place, the address of the instruction following the CPE instruction is pushed onto the stack.

Bytes/M-Cycles/T-States: 3/2/9 if transfer is not taken

2/5/10

3/5/18

if the transfer is taken

Hex Codes: EC

Flags: No flags affected.

# CPO address(16b)

**Description:** The program sequence is transferred to the address specified by the 16-bit address if parity is odd, or if the P flag = 0. If P = 1, no transfer takes place. If the transfer takes place, the address of the instruction following the CPO instruction is pushed onto the stack.

Bytes/M-Cycles/T-States: 3/2/9 if transfer is not taken

3/5/18 if the transfer is taken

Hex Codes: E4

Flags: No flags are affected.

## CZ address(16b)

**Description:** The program sequence is transferred to the address specified by the 16-bit address if zero, or if the Z flag = 1. If Z = 0, no transfer takes place. If the transfer takes place, the address of the instruction following the CZ instruction is pushed onto the stack.

Bytes/M-Cycles/T-States: 3/2/9 if transfer is not taken

3/5/18 if the transfer is taken

Hex Codes: CC

**Flags:** No flags are affected.

#### CNZ address(16b)

**Description:** The program sequence is transferred to the address specified by the 16-bit address if not zero, or if the Z flag = 0. If Z = 1, no transfer takes place. If the transfer takes place, the address of the instruction following the CNZ instruction is pushed onto the stack.

Bytes/M-Cycles/T-States: 3/2/9 if transfer is not taken

3/5/18 if the transfer is taken

Hex Codes: C4

Flags: No flags are affected.

## CMA

**Description:** The contents of the accumulator are complemented.

Bytes/M-Cycles/T-States: 1/1/4

Hex Codes: 2F

#### **CMC**

**Description:** The carry flag is complemented.

Bytes/M-Cycles/T-States: 1/1/4

Hex Codes: 3F

Flags: The CY flag is complemented. No other flags are affected.

#### CMP R

**Description:** The contents of the register are compared to the contents of the accumulator. Both contents are unaffected, and the following flags are used to show the results of the compare:

If

$$A < R$$

$CY = 1$  and  $Z = 0$

If

$$A = R$$

$CY = 0$  and  $Z = 1$

If

$$A > R$$

$CY = 0$  and  $Z = 0$

# Bytes/M-Cycles/T-States: 1/1/4

# Registers

**Flags:** S, P, and AC are also affected based upon the results of the operation, besides Z and CY.

#### CMP M

**Description:** The contents of the memory location pointed to by HL are compared to the contents of the accumulator. Both contents are unaffected, and the following flags are used to show the results of the compare:

If

$$A < R$$

$CY = 1$  and  $Z = 0$

If

$$A = R$$

$CY = 0$  and  $Z = 1$

If

$$A > R$$

$CY = 0$  and  $Z = 0$

Bytes/M-Cycles/T-States: 1/2/7

**Hex Codes: BE**

**Flags:** S, P, and AC are also affected based upon the results of the operation, besides Z and CY.

## CPI data(8b)

**Description:** The 8-bit data is compared with the contents of the accumulator. The contents of the accumulator are unaffected. The following flags are used to show the results of the compare:

If

$$A < R$$

$CY = 1$  and  $Z = 0$

If

$$A = R$$

$CY = 0$  and  $Z = 1$

If

$$A > R$$

$CY = 0$  and  $Z = 0$

Bytes/M-Cycles/T-States: 2/2/7

**Hex Codes:** FE

**Flags:** S, P, and AC are also affected based upon the results of the operation, besides Z and CY.

#### DAA

**Description:** The contents of the accumulator are converted from a binary value to two 4-bit Binary Coded Decimal (BCD) digits.

Bytes/M-Cycles/T-States: 1/1/4

Hex Codes: 27

**Flags:** S, Z, AC, P, and CY flags are affected based upon the results of the operation.

## DAD Rp

**Description:** The contents of the register pair (Rp) are added to the contents of the register pair HL. The source register pair is unchanged, and the results are stored in HL.

Bytes/M-Cycles/T-States: 1/3/10

# Register Pair

| Hex Codes: 09 | BC |

|---------------|----|

| 19            | DE |

| 29            | HL |

| 39            | SP |

**Flags:** If the result is larger than 16 bits, the CY flag is set, otherwise no flags are affected.

#### DCR R

**Description:** The contents of the register are decremented by one. The result is stored in the register.

Bytes/M-Cycles/T-States: 1/1/4

## Register

| Hex Codes: | 3D | A |

|------------|----|---|

|            | 05 | В |

|            | 0D | C |

|            | 15 | D |

|            | 1D | E |

|            | 25 | Н |

|            | 2D | L |

**Flags:** S, AC, Z, and P are affected by the results of the operation. The CY flag is not affected.

#### DCR M

**Description:** The contents of the memory location pointed to by HL is decremented by one, and the results are stored in the memory location.

Bytes/M-Cycles/T-States: 1/3/10

Hex Code: 35

**Flags:** S, AC, Z, and P are affected by the results of the operation. The CY flag is not affected.

# DCX Rp

**Description:** The contents of the register pair are decremented by 1. The result is stored in the register pair. The register pair is treated as a 16-bit number.

Bytes/M-Cycles/T-States: 1/1/6

Register Pair

Hex Codes:

0B

BC

1B

DE

2B

HL

3B

SP

Flags: No flags are affected.

DI

**Description:** The Interrupt Enable flip-flop is reset, and all of the interrupts except the TRAP interrupt are disabled.

Bytes/M-Cycles/T-States: 1/1/4

Hex Codes: F3

Flags: No flags are affected.

ΕI

**Description:** The interrupt Enable flip-flop is set and all interrupts are enabled.

Bytes/M-Cycles/T-States: 1/1/4

Hex Codes: FB

Flags: No flags are affected.

## HLT

**Description:** The MPU finishes executing the current instruction and halts any further execution. The MPU enters the Halt Acknowledge machine cycle, and Wait states are inserted in every clock period. It requires an interrupt or a reset to get the MPU out of the Halt state.

Bytes/M-Cycles/T-States: One / two or more / five or more

Hex Codes: 76

**Flags:** No flags are affected.

## IN port address(8b)

**Description:** The contents of the input port designated are read and loaded into the accumulator.

Bytes/M-Cycles/T-States: 2/3/10

Hex Codes: DB

#### INR R

**Description:** The contents of the register are incremented by one and stored in the register.

Bytes/M-Cycles/T-States: 1/1/4

# Register

Hex Codes: 3C A

04 B

0C C

14 D

1C E

24 H

2C L

**Flags:** S, Z, P, AC are affected by the results of the operation. CY is not modified.

#### INR M

**Description:** The contents of the memory location pointed to by HL are incremented by one and the result is put in the memory location.

Bytes/M-Cycles/T-States: 1/3/10

Hex Codes: 34

**Flags:** S, Z, P, and AC are affected by the results of the operation. CY is not modified.

#### INX Rp

**Description:** The contents of the register pair are incremented by 1 and stored in the register pair. The instruction views the two registers as a 16-bit number.

Bytes/M-Cycles/T-States: 1/1/6

## Register Pair

Hex Codes: 03 BC

13 DE

23 HL

33 SP

Flags: No flags are affected.

# JMP address(16b)

**Description:** The program execution is transferred to the memory address specified.

Bytes/M-Cycles/T-States: 3/3/10

Hex Codes: C3

Flags: No flags are affected.

## JC address(16b)

**Description:** Program execution is transferred to the memory address specified if the carry flag is set, or CY = 1. If CY = 0, no transfer takes place.

Bytes/M-Cycles/T-States: 3/2/7 if condition is not true

3/3/10 if condition is true

Hex Codes: DA

Flags: No flags are affected.

JNC address(16b)

**Description:** Program execution is transferred to the memory address specified if the carry flag is not set, or CY = 0. If CY = 1, no transfer takes place.

**Bytes/M-Cycles/T-States:** 3/2/7 if condition is not true

3/3/10 if condition is true

Hex Codes: D2

Flags: No flags are affected.

JP address(16b)

**Description:** Program execution is transferred to the memory address specified if positive, or S = 0. If S = 1, no transfer takes place.

Bytes/M-Cycles/T-States: 3/2/7 if condition is not true

3/3/10 if condition is true

Hex Codes: F2

Flags: No flags are affected.

JM address(16b)

**Description:** Program execution is transferred to the memory address specified if minus, or S = 1. If S = 0, no transfer takes place.

**Bytes/M-Cycles/T-States:** 3/2/7 if condition is not true

3/3/10 if condition is true

**Hex Codes: FA**

Flags: No flags are affected.

JPE address(16b)

**Description:** Program execution is transferred to the memory address specified if parity is even, or P = 1. If P = 0, no transfer takes place.

Bytes/M-Cycles/T-States: 3/2/7 if condition is not true

3/3/10 if condition is true

Hex Codes: EA

Flags: No flags are affected.

JPO address(16b)

**Description:** Program execution is transferred to the memory address specified if parity is odd, or P = 0. If P = 1, no transfer takes place.

**Bytes/M-Cycles/T-States:** 3/2/7 if condition is not true

3/3/10 if condition is true

Hex Codes: E2

## JZ address(16b)

**Description:** Program execution is transferred to the memory address

specified if zero, or Z = 1. If Z = 0, no transfer takes place.

if condition is not true Bytes/M-Cycles/T-States: 3/2/7

> 3/3/10 if condition is true

Hex Codes: CA

Flags: No flags are affected.

## INZ address(16b)

Description: Program execution is transferred to the memory address specified if not zero, or Z = 0. If Z = 1, no transfer takes place.

if condition is not true 3/2/7Bytes/M-Cycles/T-States:

> 3/3/10 if condition is true

Hex Codes: C2

Flags: No flags are affected.

# LDA address(16b)

Description: The contents of the memory location specified are

transferred to the accumulator. Bytes/M-Cycles/T-States: 3/4/13

Hex Codes: 3A

Flags: No flags are affected.

## LDAX Rp

Description: The contents of the memory location pointed to by the register pair are loaded into the accumulator.

Bytes/M-Cycles/T-States: 1/2/7

Register Pairs

Hex Codes: 0A BC

DE.

1 A

Flags: No flags are affected.

## LHLD address(16b)

**Description:** The contents of the memory location specified are loaded into register L and the contents of the next memory location are loaded into register H.

Bytes/M-Cycles/T-States: 3/5/16

Hex Codes: 2A

Flags: No flags are affected.

## LXI Rp, data(16b)

**Description:** The 16-bit data is loaded into the register pair.

Bytes/M-Cycles/T-States: 3/3/10

| Register | Pair |

|----------|------|

|----------|------|

| Hex Codes: 01 | BC |  |

|---------------|----|--|

| 11            | DE |  |

| 21            | HL |  |

| 31            | SP |  |

**Flags:** No flags are affected.

## MOV Rd, Rs

**Description:** The contents of the source register Rs are transferred into the destination register Rd.

Bytes/M-Cycles/T-States: 1/1/4

Hex Codes:

Destination Register

|   |    | ~~~~~ |    |    |    |    |    |

|---|----|-------|----|----|----|----|----|

|   | A  | В     | С  | D  | E  | H  | L  |

| A | 7F | 78    | 79 | 7A | 7B | 7C | 7D |

| В | 47 | 40    | 41 | 42 | 43 | 44 | 45 |

| С | 41 | 48    | 49 | 4A | 4B | 4C | 4D |

| D | 57 | 50    | 51 | 52 | 53 | 54 | 55 |

| E | 5F | 58    | 59 | 5A | 5B | 5C | 5D |

| Н | 67 | 60    | 61 | 62 | 63 | 64 | 65 |

| L | 6F | 68    | 69 | 6A | 6B | 6C | 6D |

Flags: No flags are affected.

## MOV M, Rs

**Description:** The contents of the source register Rs are transferred to the memory location pointed to by HL.

Bytes/M-Cycles/T-States: 1/2/7

**Hex Codes:** Source Register 77 Α 70 В 71 C72 D 73 E 74 Η 75 L

Flags: No flags are affected.

## MOV Rd, M

**Description:** The contents of the memory location pointed to by HL are transferred to the destination register.

Bytes/M-Cycles/T-States: 1/2/7

**Hex Codes:** Destination Register

7E A

46 B

4E C

| 56 | D |

|----|---|

| 5E | E |

| 66 | Н |

| 6E | L |

Flags: No flags are affected.

# MVI R, data(8b)

**Description:** The 8 bits of data are stored in the register.

Bytes/M-Cycles/T-States: 2/2/7

# Register

Hex Codes: 3E A

06 B

0E C

16 D

1E E

26 H

2E L

Flags: No flags are affected.

# MVI M, data(8b)

**Description:** The 8 bits of data are stored in the memory location pointed to by HL.

Bytes/M-Cycles/T-States: 2/3/10

Hex Codes: 36

Flags: No flags are affected.

## NOP

**Description:** No operation is performed. The instruction is fetched and decoded, but no operation is executed.

Bytes/M-Cycles/T-States: 1/1/4

Hex Codes: 00

Flags: No flags are affected.

## ORA R

**Description:** The contents of the accumulator are logically OR'd with the contents of the register. The result is stored in the accumulator.

Bytes/M-Cycles/T-States: 1/1/4

## Register

Hex Codes:

B7

A

B0

B

B1

C

B2

D

B3

E

B4

H

B5

L

**Flags:** Z, S, and P are affected based upon the operation. AC and CY are reset.

#### ORA M

**Description:** The contents of the accumulator are logically OR'd with the contents of the memory location pointed to by HL.

Bytes/M-Cycles/T-States: 1/2/7

Hex Codes: B6

**Flags:** Z, S, and P are affected based upon the operation. AC and CY are reset.

# ORI data(8b)

**Description:** The contents of the accumulator are logically OR'd with the 8 bits of data. The result is stored in the accumulator.

Bytes/M-Cycles/T-States: 2/2/7

Hex Codes: F6

**Flags:** Z, S, and P are affected based upon the operation. AC and CY are reset.

# OUT port address(8b)

**Description:** The contents of the accumulator are copied out to the output port specified.

Bytes/M-Cycles/T-States: 2/3/10

Hex Codes: D3

Flags: No flags are affected.

#### **PCHL**

**Description:** The contents of registers H and L are copied into the program counter. H is the high-order bits and L is the low-order bits.

Bytes/M-Cycles/T-States: 1/1/6

Hex Codes: E9

**Flags:** No flags are affected.

# POP Rp

**Description:** The contents of the memory location (stack) pointed to by the stack pointer are copied to the low-order register of the register pair. (C, E, L, and flags.) The stack pointer is then incremented and the contents of that memory location being pointed to are copied to the high-order register of the register pair.

## Bytes/M-Cycles/T-States: 1/3/10

Register

Hex Codes: C1 BC

D1 DE

E1 HL

F1 PSW

Flags: No flags are affected.

#### PUSH Rp

**Description:** The contents of the register pair are copied into the stack. The high-order register (B, D, H, A) is put on the stack first, then the contents of the low-order register (C, E, L, flags) are put onto the stack.

Bytes/M-Cycles/T-States: 1/3/12

Register Pair

Hex Codes: C5 B

D5 D E5 H

F5 PSW

Flags: No flags are affected.

#### RAL

**Description:** The contents of the accumulator are rotated left by one position through the carry flag.

Bytes/M-Cycles/T-States: 1/1/4

Hex Codes: 17

**Flags:** CY is modified according to bit D7. S, Z, P, and AC are not affected.

#### RAR

**Description:** The contents of the accumulator are rotated right by one position through the carry flag.

Bytes/M-Cycles/T-States: 1/1/4

Hex Codes: 1F

**Flags:** CY is modified according to bit D0. S, Z, P, and AC are not affected.

#### **RLC**

**Description:** The contents of the accumulator are rotated left one position. Bit D7 is placed in both D0 and CY.

Bytes/M-Cycles/T-States: 1/1/4

Hex Codes: 07

**Flags:** CY is modified according to bit D7. S, Z, P, and AC are not affected.

## **RRC**

**Description:** The contents of the accumulator are rotated right by 1 bit. Bit D0 is placed in both D7 and CY at the same time.

Bytes/M-Cycles/T-States: 1/1/4

Hex Codes: 0F

**Flags:** CY is modified according to bit D0. S, Z, P, and AC are not affected.

#### RET

**Description:** The program sequence is transferred from the subroutine to the calling program. The two bytes from the top of the stack are copied into the Program Counter and this is the address that program execution begins.

Bytes/M-Cycles/T-States: 1/3/10

Hex Codes: C9

Flags: No flags are affected.

RC

**Description:** The program sequence is transferred from the subroutine to the calling program if the carry flag is set, or CY = 1. If CY = 0, no transfer takes place.

**Bytes/M-Cycles/T-States:** 1/1/6 if condition is not true

1/3/12 if condition is true

Hex Codes: D8

Flags: No flags are affected.

**RNC**

**Description:** The program sequence is transferred from the subroutine to the calling program if the carry flag is not set, or CY = 0. If CY = 1, no transfer takes place.

Bytes/M-Cycles/T-States: 1/1/6 if condition is not true

1/3/12 if condition is true

Hex Codes: D0

Flags: No flags are affected.

RP

**Description:** the program sequence is transferred from the subroutine to the calling program if positive, or S = 0. If S = 1, no transfer takes place.

Bytes/M-Cycles/T-States: 1/1/6 if condition is not true

1/3/12 if condition is true

Hex Codes: FO

Flags: No flags are affected.

RM

**Description:** The program sequence is transferred from the subroutine to the calling program if minus, or S = 1. If S = 0, no transfer takes place.

Bytes/M-Cycles/T-States: 1/1/6 if condition is not true

1/3/12 if condition is true

Hex Codes: F8

Flags: No flags are affected.

**RPE**

**Description:** The program sequence is transferred from the subroutine to the calling program if the parity is even, or P = 1. If P = 0, no transfer takes place.

Bytes/M-Cycles/T-States: 1/1/6 if condition is not true

1/3/12 if condition is true

Hex Codes: E8

**RPO**

**Description:** The program sequence is transferred from the subroutine to the calling program if the parity is odd, or P = 0. If P = 1, no transfer takes place.

Bytes/M-Cycles/T-States: 1/1/6 if condition is not true

1/3/12 if condition is true

Hex Codes: E0

Flags: No flags are affected

RZ

**Description:** The program sequence is transferred from the subroutine to the calling program if zero, or Z = 1. If Z = 0, no transfer takes place.

Bytes/M-Cycles/T-States: 1/1/6 if condition is not true

1/3/12 if condition is true

Hex Codes: C8

Flags: No flags are affected.

RNZ

**Description:** The program sequence is transferred from the subroutine to the calling program if not zero, or Z = 0. If Z = 1, no transfer takes place.

Bytes/M-Cycles/T-States: 1/1/6 if condition is not true

1/3/12 if condition is true

Hex Codes: C0

Flags: No flags are affected.

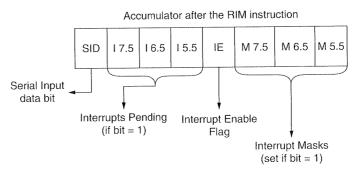

**RIM**

**Description:** This instruction is used to both read in the status of interrupts 7.5, 6.5, and 5.5, as well as to read in the serial input data bit. An 8-bit word is read in and stored in the accumulator. The layout of that word is shown in Figure A1-1.

Figure A1-1 ■ The RIM instruction layout in the accumulator

Bytes/M-Cycles/T-States: 1/1/4

Hex Codes: 20

RST n (where n = 0 - 7)

**Description:** This instruction operates like a call instruction that goes to one of eight predetermined memory locations on page 0. Each instruction (RST 0–RST 7) goes to a specific address listed next.

| Instruction | Restart Address |

|-------------|-----------------|

| RST 0       | 0000            |

| RST 1       | 0008            |

| RST 2       | 0010            |

| RST 3       | 0018            |

| RST 4       | 0020            |

| RST 5       | 0028            |

| RST 6       | 0030            |

| RST 7       | 0038            |

Bytes/M-Cycles/T-States: 1/3/12

| Hex Codes: C7 | RST 0 |

|---------------|-------|

| CF            | RST 1 |

| D7            | RST 2 |

| DF            | RST 3 |

| E7            | RST 4 |

| EF            | RST 5 |

| F7            | RST 6 |

| FF            | RST 7 |

Flags: No flags are accepted.

## SBB R

**Description:** The contents of the register and the borrow flag are subtracted from the contents of the accumulator and the results are stored in the accumulator.

Bytes/M-Cycles/T-States: 1/1/4

|                   |    | Registe |

|-------------------|----|---------|

| <b>Hex Codes:</b> | 9F | A       |

|                   | 98 | В       |

|                   | 99 | С       |

|                   | 9A | D       |

|                   | 9B | E       |

|                   | 9C | H       |

|                   | 9D | L       |

Flags: All flags are affected based upon the results of the operation.

#### SBB M

**Description:** The contents of the memory location pointed to by HL and the borrow flag are subtracted from the contents of the accumulator. The results are then stored in the accumulator.

Bytes/M-Cycles/T-States: 1/2/7

Hex Codes: 9E

Flags: All flags are affected based upon the results of the operation.

## SBI data(8b)

**Description:** The 8 bits of data and the borrow flag are subtracted from the accumulator and the results are stored in the accumulator.

Bytes/M-Cycles/T-States: 2/2/7

Hex Codes: DE

Flags: All flags are affected based upon the results of the operation.

# SHLD address(16b)

**Description:** The contents of register L are stored at the memory location specified and the contents of register H are stored at the next memory location by incrementing the operand by 1.

Bytes/M-Cycles/T-States: 3/5/16

Hex Codes: 22

Flags: No flags are affected.

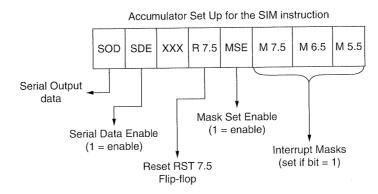

#### SIM

**Description:** This is an instruction that is used to set the interrupt masks as well as set the serial output data bit. The accumulator is laid out as shown in Figure A1-2.

Figure A1-2 ■ The SIM instruction accumulator layout

Bytes/M-Cycles/T-States: 1/1/4

Hex Codes: 30

Flags: No flags are affected.

## **SPHL**

**Description:** The contents of registers H and L are loaded into the Stack Pointer. H has the high-order part of the address, while L has the low-order portion.

Bytes/M-Cycles/T-States: 1/1/6

Hex Codes: F9

## STA address(16b)

**Description:** The contents of the accumulator are stored at the

memory location specified.

Bytes/M-Cycles/T-States: 3/4/13

Hex Codes: 32

Flags: No flags are affected.

# STAX Rp (only BC or DE)

**Description:** The contents of the accumulator are stored at the memory location pointed to by the register pair. The contents of the accumulator are not affected.

Bytes/M-Cycles/T-States: 1/2/7

Register Pair

Hex Codes: 02 BC

12 DE

Flags: No flags are affected.

## STC

**Description:** The carry flag, CY, is set to 1.

Bytes/M-Cycles/T-States: 1/1/4

Hex Codes: 37

Flags: Only the CY flag is affected.

#### SUB R

**Description:** The contents of the register are subtracted from the accumulator and the result is stored in the accumulator.

Bytes/M-Cycles/T-States: 1/1/4

Register

Hex Codes: 97 A

90 B

90 B91 C

92 D

93 E

94 H

95 L

Flags: All flags are affected by the result of the operation.

#### SUB M

**Description:** The contents of the memory location pointed to by HL are subtracted from the accumulator and the result is stored in the accumulator.

Bytes/M-Cycles/T-States: 1/2/7

Hex Codes: 96

**Flags:** All flags are affected by the result of the operation.

# SUI data(8b)

**Description:** The 8-bit data is subtracted from the contents of the accumulator. The result is stored in the accumulator.

Bytes/M-Cycles/T-States: 2/2/7

Hex Codes: D6

Flags: All flags are affected by the result of the operation.

#### **XCHG**

**Description:** The contents of register H and register D are exchanged, and the contents of register L and register E are exchanged.

Bytes/M-Cycles/T-States: 1/1/4

**Hex Codes: EB**

Flags: No flags are affected.

#### XRA R

**Description:** The contents of the register are Exclusive OR'd with the contents of the accumulator. The results are then stored in the accumulator.

Bytes/M-Cycles/T-States: 1/1/4

## Register

Hex Codes: AF A

A8 B

A9 C

AA D

AB E

AC H

AD L

**Flags:** Z, S, and P are affected based upon the operation. CY and AC are reset.

## XRA M

**Description:** The contents of the memory location pointed to by HL are Exclusive OR'd with the contents of the accumulator. The results are stored in the accumulator.

Bytes/M-Cycles/T-States: 1/2/7

**Hex Codes: AE**

**Flags:** Z, S, and P are affected based upon the operation. CY and AC are reset.

## XRI data(8b)

**Description:** The 8 bits of data are Exclusive OR'd with the contents of the accumulator. The results are then stored in the accumulator.

Bytes/M-Cycles/T-States: 2/2/7

**Hex Codes: EE**

**Flags:** Z, S, and P are affected based upon the operation. CY and AC are reset.

# XTHL

**Description:** The contents of the L register are exchanged with the stack location pointed to by the stack pointer. The contents of the H register are exchanged with the stack location pointed to by the stack pointer +1. The stack pointer remains unchanged.

Bytes/M-Cycles/T-States: 1/5/16

Hex Codes: E3