#### NMK20603 Computer Architecture

## Introduction to CAD Tools and HDL

#### Computer Aided Design

- CAD tools (software)

- ⇒ used in various fields

- → E&E

- → Mechanical

- → Civil

- Common CAD-based design flow:

- ⇒ Design entry (input)

- ⇒ Design check (optional)

- ⇒ Design simulation/synthesis (process)

# Design Entry @ Representation

- Classic methods:

- ⇒ Graphical Schematic

- ⇒ Text Netlist, HDL

- Not-so-classic method:

- ⇒ Abstract representation

- → e.g. state diagrams

### <a>Digital</a>

Systems

Design?

#### Usually involves HDL

#### Hardware Description Language

- HDL code ... not program!

- ⇒ text-encoding of system

- ⇒ describe structure / function

- Mostly used HDL:

- ⇒ VHDL (VHSIC HDL)

- ⇒ Verilog HDL

Most industry-standard tools support both

##

- strongly typed, verbose

- precise represention

- case in-sensitive

- system level integration

## Verilog

- ► C-like standard (simple?)

- easier for entry-level

- case sensitive

- simulation-friendly

#### VHDL vs Verilog

- ▶ Both have strength/weakness

- Some uses both!

- ▶ We choose Verilog

#### HDL

### Coding Style

- Structural

- ⇒ Specify exact electrical lines

- → Absolutely synthesizable

- Register Transfer Level @ RTL

- ⇒ Specify logic functions

- → Mostly synthesizable

- → May not be optimized

- Behavioral

- ⇒ Specify abstract behavior

- → May NOT be synthesizable

- → OK for behavior verification

# ✓ Will mostly do structural & RTL

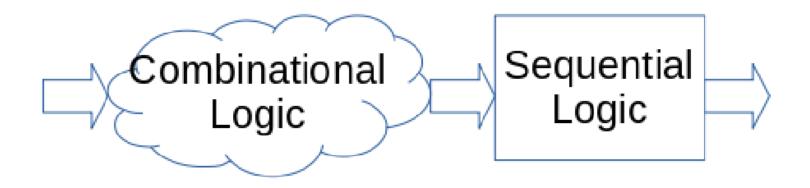

#### Digital systems

- ▶ logic gates (combinational)

- flip-flops (sequential)

### Structure!

#### ⇒ Synthesizable!

### Design Simulation & Synthesis (Processing)

### Simulation tools for HDL-based design

- Icarus Verilog

- → Open Source

- → Cross Platform

#### ⇒ Verilog compiler and simulator ONLY

- ModelSim

- → from Mentor Graphics

- → now, Siemens

⇒ Complete Design Environment Editor/Simulator/WF Viewer

#### Happy Coding!