## PGT104 – Digital Electronics

## Part 2 – Logic Gates

Disclaimer:

•Most of the contents (if not all) are extracted from resources available for Digital Fundamentals 10<sup>th</sup> Edition

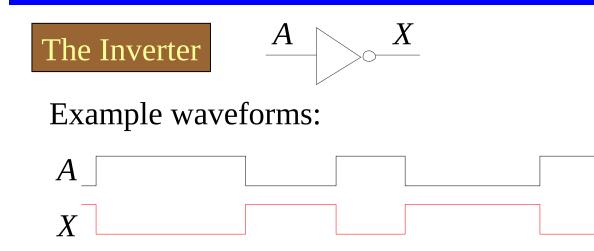

The inverter performs the Boolean **NOT** operation. When the input is LOW, the output is HIGH; when the input is HIGH, the output is LOW.

| Input               | Output             |  |  |  |

|---------------------|--------------------|--|--|--|

| A                   | X                  |  |  |  |

| LOW (0)<br>HIGH (1) | HIGH (1)<br>LOW(0) |  |  |  |

The **NOT** operation (complement) is shown with an overbar. Thus, the Boolean expression for an inverter is  $X = \overline{A}$ .

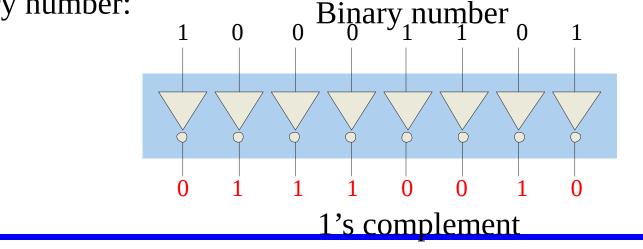

A group of inverters can be used to form the 1's complement of a binary number: Binary number

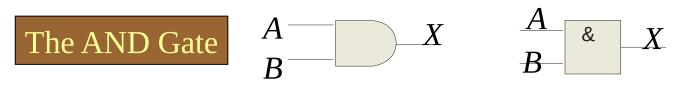

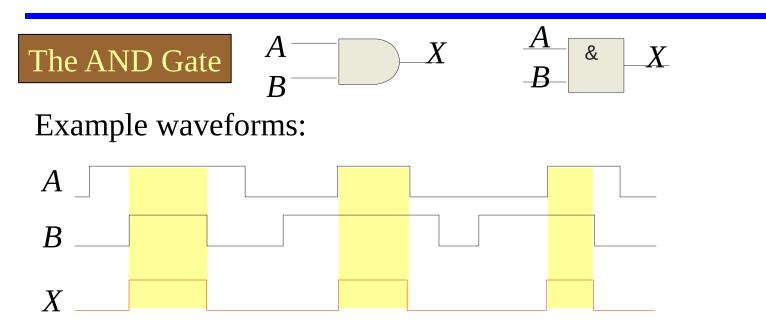

The **AND gate** produces a HIGH output when all inputs are HIGH; otherwise, the output is LOW. For a 2-input gate,

the truth table is

| Inp | outs | Output |

|-----|------|--------|

| Α   | В    | X      |

| 0   | 0    | 0      |

| 0   | 1    | 0      |

| 1   | 0    | 0      |

| 1   | 1    | 1      |

The **AND** operation is usually shown with a dot between the variables but it may be implied (no dot). Thus, the AND operation is written as  $X = A \cdot B$  or X = AB.

The AND operation is used in computer programming as a selective mask. If you want to retain certain bits of a binary number but reset the other bits to 0, you could set a mask with 1's in the position of the retained bits.

Example If the binary number 10100011 is ANDed with the mask 00001111, what is the result? 00000011

# Checkpoint

- Imagine a 4-bit counter (output C<sub>3</sub>C<sub>2</sub>C<sub>1</sub>C<sub>0</sub>) with any 2-bit output fed into a 2-input AND gate:

- draw timing diagram for the circuit if bits  $C_3$  and  $C_1$  are used as inputs, and the counter is counting up

- what about other pairs?

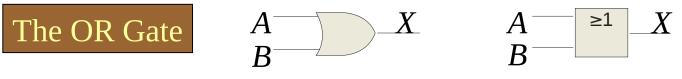

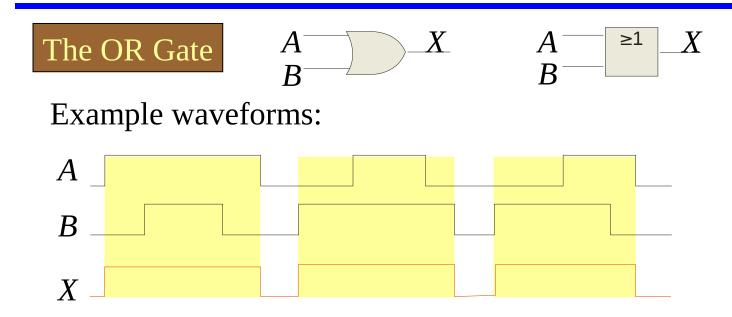

The **OR gate** produces a HIGH output if any input is HIGH; if all inputs are LOW, the output is LOW. For a 2-input gate, the truth table is

| Inp | outs | Output |

|-----|------|--------|

| Α   | В    | X      |

| 0   | 0    | 0      |

| 0   | 1    | 1      |

| 1   | 0    | 1      |

| 1   | 1    | 1      |

The **OR** operation is shown with a plus sign (+) between the variables. Thus, the OR operation is written as X = A + B.

The OR operation can be used in computer programming to set certain bits of a binary number to 1.

ASCII letters have a 1 in the bit 5 position for lower case letters and a 0 in this position for capitals. (Bit positions are numbered from right to left starting with 0.) What will be the result if you OR an ASCII letter with the 8-bit mask 00100000?

The resulting letter will be lower case.

Example

# Checkpoint

- Imagine a 4-bit counter (output C<sub>3</sub>C<sub>2</sub>C<sub>1</sub>C<sub>0</sub>) with any 2-bit output fed into a 2-input OR gate:

- draw timing diagram for the circuit if bits  $C_2$  and  $C_1$  are used as inputs, and the counter is counting down

- what about other pairs?

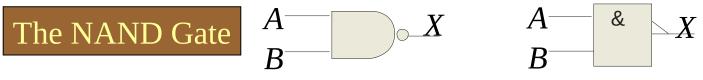

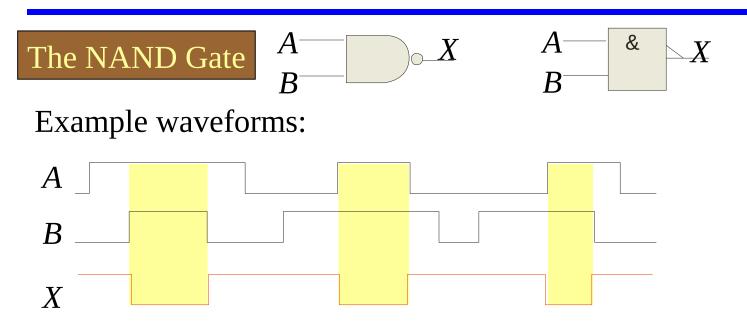

The **NAND gate** produces a LOW output when all inputs are HIGH; otherwise, the output is HIGH. For a 2-input

gate, the truth table is

| Inp | uts | Output |

|-----|-----|--------|

| Α   | В   | X      |

| 0   | 0   | 1      |

| 0   | 1   | 1      |

| 1   | 0   | 1      |

| 1   | 1   | 0      |

The **NAND** operation is shown with a dot between the variables and an overbar covering them. Thus, the NAND operation is written as  $X = \overline{A \cdot B}$  (Alternatively,  $X = \overline{AB}$ .)

The NAND gate is particularly useful because it is a "universal" gate – all other basic gates can be constructed from NAND gates.

How would you connect a 2-input NAND gate to form a basic inverter?

Trivia

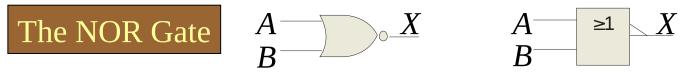

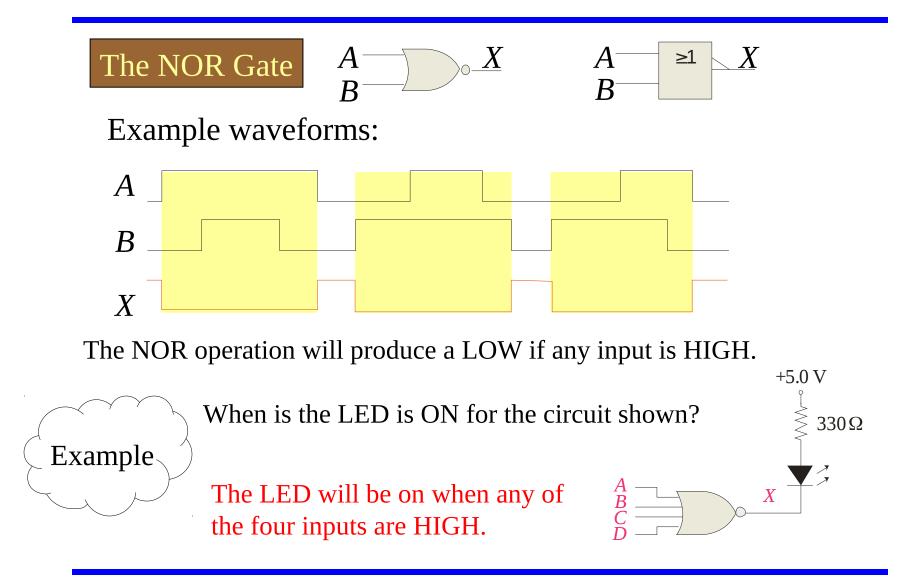

The **NOR gate** produces a LOW output if any input is HIGH; if all inputs are HIGH, the output is LOW. For a 2-input gate, the truth table is

| Inp | outs | Output |

|-----|------|--------|

| Α   | В    | X      |

| 0   | 0    | 1      |

| 0   | 1    | 0      |

| 1   | 0    | 0      |

| 1   | 1    | 0      |

The **NOR** operation is shown with a plus sign (+) between the variables and an overbar covering them. Thus, the NOR operation is written as  $X = \overline{A + B}$ .

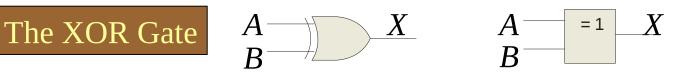

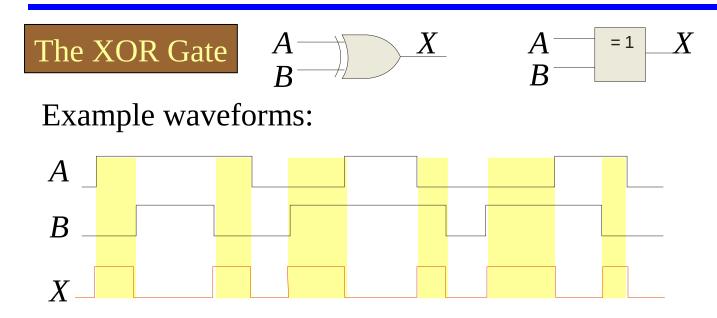

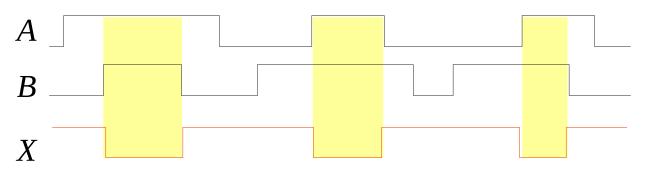

The **XOR gate** produces a HIGH output only when both inputs are at opposite logic levels. The truth table is

| Inp | outs | Output |

|-----|------|--------|

| Α   | В    | X      |

| 0   | 0    | 0      |

| 0   | 1    | 1      |

| 1   | 0    | 1      |

| 1   | 1    | 0      |

The **XOR** operation is written as  $X = \overline{AB} + A\overline{B}$ . Alternatively, it can be written with a circled plus sign between the variables as  $X = A \bigoplus B$ .

Notice that the XOR gate will produce a HIGH only when exactly one input is HIGH.

If the *A* and *B* waveforms are both inverted for the above waveforms, how is the output affected?

There is no change in the output.

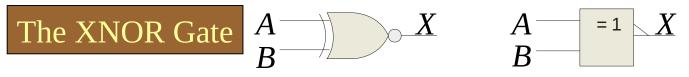

The **XNOR gate** produces a HIGH output only when both inputs are at the same logic level. The truth table is

| Inp | outs | Output |

|-----|------|--------|

| Α   | В    | X      |

| 0   | 0    | 1      |

| 0   | 1    | 0      |

| 1   | 0    | 0      |

| 1   | 1    | 1      |

The **XNOR** operation shown as  $X = \overline{AB} + AB$ . Alternatively, the XNOR operation can be shown with a circled dot between the variables. Thus, it can be shown as  $X = A \bigcirc B$ .

Notice that the XNOR gate will produce a HIGH when both inputs are the same. This makes it useful for comparison functions.

Example

If the *A* waveform is inverted but *B* remains the same, how is the output affected?

The output will be inverted.

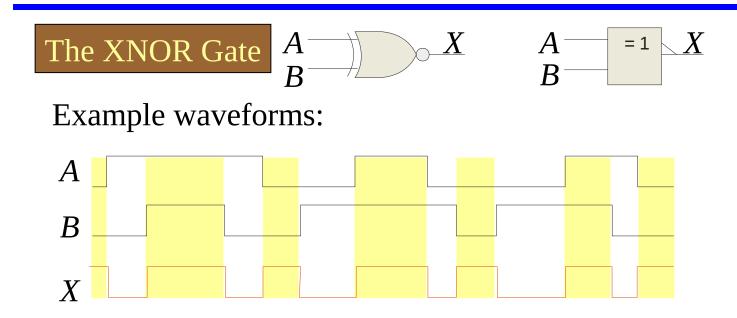

Two major fixed function logic families are TTL and CMOS. A third technology is BiCMOS, which combines the first two. Packaging for fixed function logic is shown.

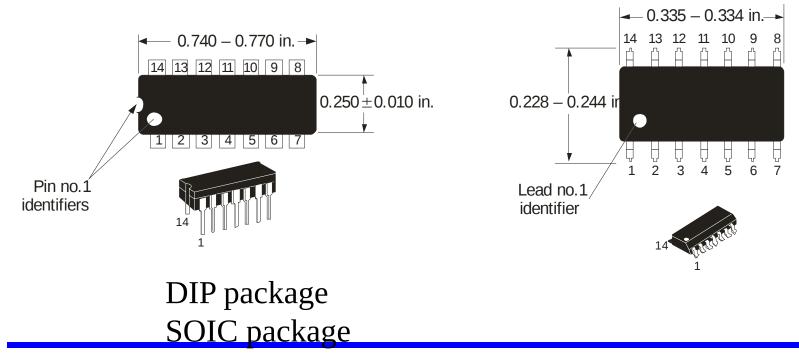

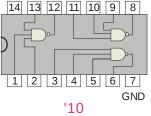

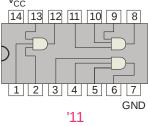

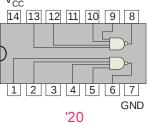

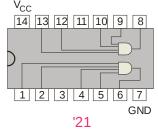

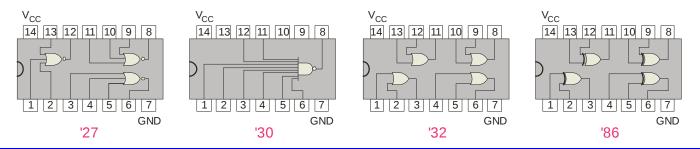

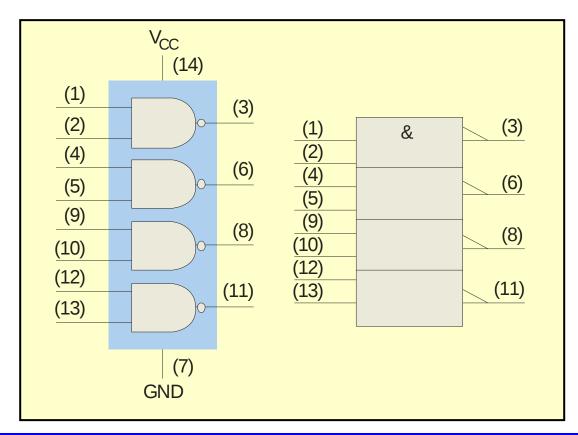

# Some common gate configurations are shown. $V_{CC}$

Logic symbols show the gates and associated pin numbers.

Data sheets include limits and conditions set by the manufacturer as well as DC and AC characteristics. For example, some maximum ratings for a 74HC00A are:

MAXIMUM RATINGS

| Symbol           | Parameter                                                | Value                           | Unit |

|------------------|----------------------------------------------------------|---------------------------------|------|

| V <sub>CC</sub>  | DC Supply Voltage (Referenced to GND)                    | -0.5 to + 7.0 V                 | V    |

| Vin              | DC InputVoltage (Referenced to GND)                      | -0.5 to V <sub>CC</sub> +0.5 V  | V    |

| V <sub>out</sub> | DC Output Voltage (Referenced to GND)                    | – 0.5 to V <sub>CC</sub> +0.5 V | / V  |

| l in             | DC Input Current, per pin                                | ±20                             | mA   |

| lout             | DC Output Current, per pin                               | ±25                             | mA   |

| I <sub>CC</sub>  | DC Supply Current, $V_{CC}$ and GND pins                 | ±50                             | mA   |

| PD               | Power Dissipation in Still Air, Plastic or Ceramic DIP + | 750                             | mW   |

|                  | SOIC Package †                                           | 500                             |      |

|                  | TSSOP Package †                                          | 450                             |      |

| T <sub>stg</sub> | Storage Temperature                                      | -65 to + 150                    | °C   |

| TL               | Lead Temperature, 1 mm from Case for 10 Seconds          |                                 | ℃    |

|                  | Plastic DIP, SOIC, or TSSOP Package                      | 260                             |      |

|                  | Ceramic DIP                                              | 300                             |      |

#### The truth table for a 2-input AND gate is

|    | Inputs |      | Output | -  | Inputs |      | Output |

|----|--------|------|--------|----|--------|------|--------|

|    | A      | В    | X      | -  | Α      | В    | X      |

| a. | 0      | 0    | 0      | b. | 0      | 0    | 1      |

|    | 0      | 1    | 1      | 0. | 0      | 1    | 0      |

|    | 1      | 0    | 1      |    | 1      | 0    | 0      |

|    | 1      | 1    | 0      |    | 1      | 1    | 0      |

| _  |        |      | ·      | -  |        |      |        |

|    | Inp    | outs | Output |    | Inp    | outs | Output |

| _  | A      | В    | X      | -  | Α      | В    | X      |

| C. | 0      | 0    | 0      | d. | 0      | 0    | 0      |

|    | 0      | 1    | 0      |    | 0      | 1    | 1      |

|    | 1      | 0    | 0      |    | 1      | 0    | 1      |

|    | 1      | 1    | 1      |    | 1      | 1    | 1      |

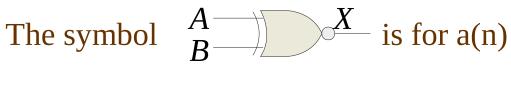

#### The truth table for a 2-input NOR gate is

|    | Inputs |      | Output | -  | Inputs |      | Output |

|----|--------|------|--------|----|--------|------|--------|

| a. | A      | В    | X      |    | Α      | В    | X      |

|    | 0      | 0    | 0      | b. | 0      | 0    | 1      |

|    | 0      | 1    | 1      | 0. | 0      | 1    | 0      |

|    | 1      | 0    | 1      |    | 1      | 0    | 0      |

|    | 1      | 1    | 0      |    | 1      | 1    | 0      |

| -  |        |      | ·<br>  | -  |        |      |        |

|    | Inp    | outs | Output |    | Inp    | outs | Output |

| -  | Α      | В    | X      |    | Α      | В    | X      |

|    | 0      | 0    | 0      |    | 0      | 0    | 0      |

| С. | 0      | 1    | 0      | d. | 0      | 1    | 1      |

|    | 1      | 0    | 0      |    | 1      | 0    | 1      |

| _  | 1      | 1    | 1      | _  | 1      | 1    | 1      |

#### The truth table for a 2-input XOR gate is

|    | Inputs |   | Output |    | Inputs |      | Output |

|----|--------|---|--------|----|--------|------|--------|

| a. | Α      | В | X      |    | Α      | В    | X      |

|    | 0      | 0 | 0      | b. | 0      | 0    | 1      |

|    | 0      | 1 | 1      | υ. | 0      | 1    | 0      |

|    | 1      | 0 | 1      |    | 1      | 0    | 0      |

|    | 1      | 1 | 0      |    | 1      | 1    | 0      |

| -  |        |   |        |    |        |      |        |

|    | Inputs |   | Output |    | Inp    | outs | Output |

| -  | Α      | В | X      |    | Α      | В    | X      |

| _  | 0      | 0 | 0      |    | 0      | 0    | 0      |

| С. | 0      | 1 | 0      | d. | 0      | 1    | 1      |

|    | 1      | 0 | 0      |    | 1      | 0    | 1      |

|    | 1      | 1 | 1      |    | 1      | 1    | 1      |

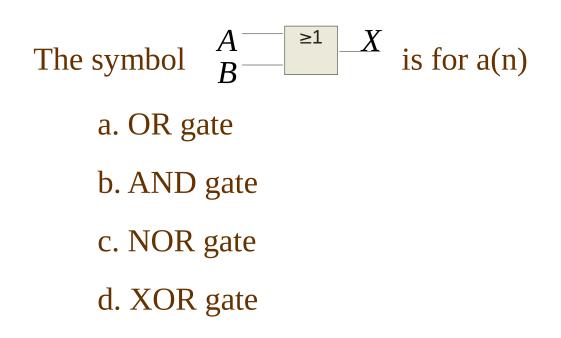

a. OR gate

- b. AND gate

- c. XNOR gate

- d. XOR gate

A logic gate that produces a HIGH output only when all of its inputs are HIGH is a(n)

a. OR gate

b. AND gate

c. NOR gate

d. NAND gate

The expression  $X = A \oplus B$  means a. A OR Bb. A AND Bc. A XOR Bd. A XNOR B

A 2-input gate produces the output shown. (*X* represents the output.) This is a(n)

a. OR gate

b. AND gate

c. NOR gate

d. NAND gate

A 2-input gate produces a HIGH output only when the inputs agree. This type of gate is a(n)

a. OR gate

b. AND gate

c. NOR gate

d. XNOR gate